Перспективы развития статической регистровой памяти или

«Этот безумный-безумный мир».

В настоящее время небывалое распространение получила так называемая динамическая или вернее емкостная память. Данный вид памяти не смотря на свои недостатки и неудобства подключения из-за мультиплексной шины адреса почти полностью занял все позиции на рынке памяти. И вообще сейчас подавляющий совокупный объем памяти всех устройств в мире является памятью именно динамической. Причиной сего называют ее низкую стоимость. Не будем сосредотачиваться на необходимости её периодической регенерации, мультиплексной шине адреса и атавистичных сигналах RAS и CAS.

Сосредоточимся именно на относительной стоимости ячейки памяти.

Этот параметр напрямую зависит от площади на кристалле, занимаемой одной ячекой. Как известно, затвор запоминающего транзистора ячейки динамической памяти занимает довольно приличную площадь, достаточную для размещения нескольких обычных транзисторов, выполненных по соответствующей технологии для обеспечения необходимой емкости образуемого им конденсатора.

Странно, неужели на этой площади не сможет разместиться одна ячейка статической памяти ?

Но хотелось бы упомянуть о импульсных токах, потребляемых современными статическими запоминающими устройствами при записи. Представляете, когда ячейка со стандартной схемой насильно переводится в неопределенное состояние и дальше… Входной сигнал подается на выход! И чем больше тактовая частота … Словом у меня поджилки трясутся о мыслях, что там происходит в данный момент! Не уже ли никто не пытался обойти данную проблему? А когда происходит элементарная подача напряжения питания на выключенную перед этим схему? В данной ситуации оказываются все ячейки! Вспомним про ненавистный тиристорный эффект в микросхеме КР537РУ10. В результате получаем неадекватные эмоции инженера проектировщика при попытке проектирования новых микросхем. В итоге становится понятным, что засилье динамической памяти на мировом рынке – проблема чисто психологического порядка.

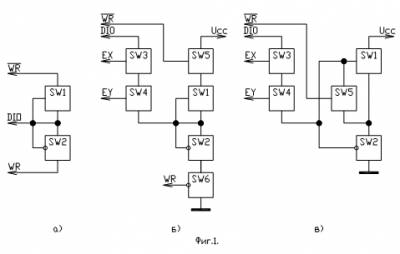

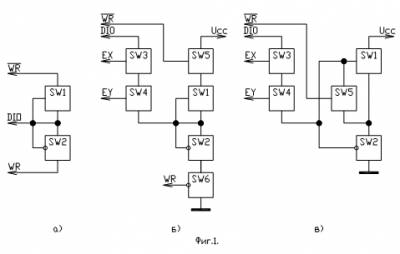

Но все рано не понятно упорное нежелание обойти эту проблему. В итоге родились ряд следующих предложений. Первое: Использовать каскад из последовательно включенных ключей, один с прямым, второй с инверсным входом управления, замкнутыми на среднюю точку между ними (рис. 1а) для хранения одного бита двоичной информации.

В этом случае питание подается через сигналы WR’ и WR. При отключении или точнее изоляции их от питающих напряжений возможно кратковременное хранение информации, как в ячейке динамической памяти, при этом возможна также перезапись. Данные снимаются при чтении или подаются во время записи прямо с/на среднюю точку. С этого в принципе все началось.

Для использования триггера в матрице запоминающего устройства необходимы для каждой ячейки дополнительно четыре (рис. 1б) или три (рис. 1в) ключа для выборки по координатным осям и управления записью.

В этом случае питание подается через сигналы WR’ и WR. При отключении или точнее изоляции их от питающих напряжений возможно кратковременное хранение информации, как в ячейке динамической памяти, при этом возможна также перезапись. Данные снимаются при чтении или подаются во время записи прямо с/на среднюю точку. С этого в принципе все началось.

Для использования триггера в матрице запоминающего устройства необходимы для каждой ячейки дополнительно четыре (рис. 1б) или три (рис. 1в) ключа для выборки по координатным осям и управления записью.

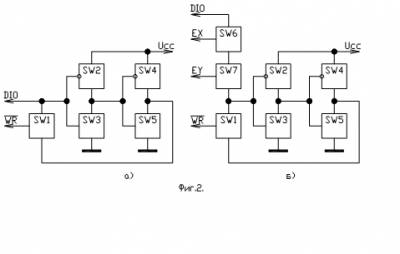

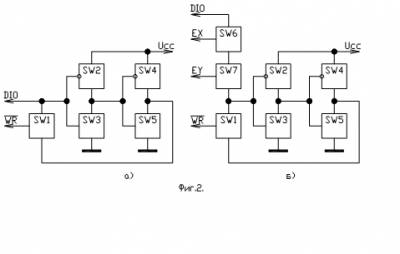

Рис. 1, 2: Примеры реализации ячеек памяти на ключах (SW), в качестве которых обычно используются полевые транзисторы.

Рис. 1, 2: Примеры реализации ячеек памяти на ключах (SW), в качестве которых обычно используются полевые транзисторы.

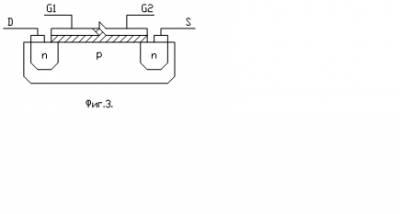

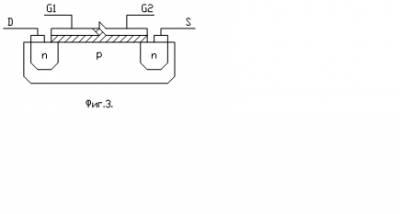

Рис. 3: Полевой двухзатворный транзистор, позволяющий скомпоновать два транзистора в один.

Возможна реализация подобной ячейки на КМДП-транзисторах со встроенным каналом. Ключи обрамления могут представлять собой обычные КМДП-транзисторы с индуцированным каналом, реализация которых особенно проста. Для реализации на КМДП-транзисторах с индуцированным каналом необходимо добавить еще один каскад (рис.2а, на рис. 2б показана схема с дополнительными ключами для двухкоординатной выборки). Ключи для двухкоординатной выборки и дополнительные ключи на рис. 1б могут быть при применении двухзатворных МДП-транзисторов с последовательно расположенными затворами (рис.3) сгруппированы попарно, что уменьшит количество ключей или транзисторов для ячейки на рис. 1б до трех.

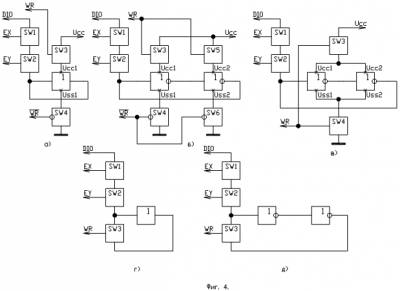

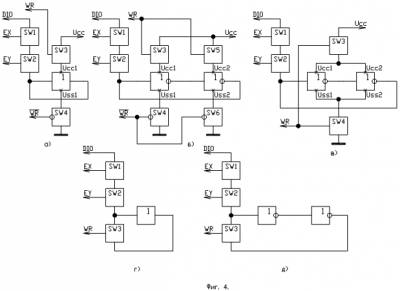

Второе: разложить все по кирпичикам дальше. Как видно, каскады на фиг. 1 представляют собой формирователи без инверсии, а на фиг. 2 — инверторы, в результате получаем схемы на фиг. 4. На фиг. 4а и 4б нижние ключи нарисованы с инверсным управлением.

Рис. 3: Полевой двухзатворный транзистор, позволяющий скомпоновать два транзистора в один.

Возможна реализация подобной ячейки на КМДП-транзисторах со встроенным каналом. Ключи обрамления могут представлять собой обычные КМДП-транзисторы с индуцированным каналом, реализация которых особенно проста. Для реализации на КМДП-транзисторах с индуцированным каналом необходимо добавить еще один каскад (рис.2а, на рис. 2б показана схема с дополнительными ключами для двухкоординатной выборки). Ключи для двухкоординатной выборки и дополнительные ключи на рис. 1б могут быть при применении двухзатворных МДП-транзисторов с последовательно расположенными затворами (рис.3) сгруппированы попарно, что уменьшит количество ключей или транзисторов для ячейки на рис. 1б до трех.

Второе: разложить все по кирпичикам дальше. Как видно, каскады на фиг. 1 представляют собой формирователи без инверсии, а на фиг. 2 — инверторы, в результате получаем схемы на фиг. 4. На фиг. 4а и 4б нижние ключи нарисованы с инверсным управлением.

Рис. 4: Дополнительные примеры реализации ячеек статической памяти на инверторах и прямых формирователях, позволяющие не устраивать конфликты на шинах.

Для возможности объединения ключей с помощью двухзатворных транзисторов, т.е. при отсутствии оной они могут быть и с прямыми входами.

В отдаленной перспективе, если указанные схемы используются в устройствах с иным принципом действия, например на биполярных транзисторах или оптических ключах, то при отсутствии эффекта емкости на входах элементов необходимо сигналы WR и WR’ тоже подавать через схемы управления, аналогично линии DIO (один разрешающий ключ для регистра или последовательные два ключа для двукоординатной выборки).

В итоге получаем чуть ли не идеал регистровой памяти на любой вкус по цене динамической. Конечно же при наличии желания производителя! А если на этот раз уже принять внимание упомянутые недостатки специфического интерфейса динамической памяти и протокола общения с ней, которые вносят свою лепту в увеличение тока потребления системы, а так же в ограничение ее быстродействия, то получаем … Нет я не буду дальше продолжать из-за скромности! Предложу это сделать читателю, так как понимаю, что я не один, что дальше возможно находятся еще неизведанные пространства познания и читатель тоже наверняка хочет почувствовать радость первооткрывателя.

1. Принципы функционирования SRAM. Крис Касперски (Ссылка citforum.ru/book/optimize/sdram.shtml );

2. D-триггер или ячейка регистра/памяти (Ссылка timeinventor.com/news.php?readmore=118 ).

Ссылки:

1. http://timeinventor.com/news.php?readmore=118 ;

2. http://technic.itizdat.ru/docs/mer/FIL13208061890N727706001/ ;

3. http://www.membrana.ru/particle/17550 .

Рис. 4: Дополнительные примеры реализации ячеек статической памяти на инверторах и прямых формирователях, позволяющие не устраивать конфликты на шинах.

Для возможности объединения ключей с помощью двухзатворных транзисторов, т.е. при отсутствии оной они могут быть и с прямыми входами.

В отдаленной перспективе, если указанные схемы используются в устройствах с иным принципом действия, например на биполярных транзисторах или оптических ключах, то при отсутствии эффекта емкости на входах элементов необходимо сигналы WR и WR’ тоже подавать через схемы управления, аналогично линии DIO (один разрешающий ключ для регистра или последовательные два ключа для двукоординатной выборки).

В итоге получаем чуть ли не идеал регистровой памяти на любой вкус по цене динамической. Конечно же при наличии желания производителя! А если на этот раз уже принять внимание упомянутые недостатки специфического интерфейса динамической памяти и протокола общения с ней, которые вносят свою лепту в увеличение тока потребления системы, а так же в ограничение ее быстродействия, то получаем … Нет я не буду дальше продолжать из-за скромности! Предложу это сделать читателю, так как понимаю, что я не один, что дальше возможно находятся еще неизведанные пространства познания и читатель тоже наверняка хочет почувствовать радость первооткрывателя.

1. Принципы функционирования SRAM. Крис Касперски (Ссылка citforum.ru/book/optimize/sdram.shtml );

2. D-триггер или ячейка регистра/памяти (Ссылка timeinventor.com/news.php?readmore=118 ).

Ссылки:

1. http://timeinventor.com/news.php?readmore=118 ;

2. http://technic.itizdat.ru/docs/mer/FIL13208061890N727706001/ ;

3. http://www.membrana.ru/particle/17550 .

|

В этом случае питание подается через сигналы WR’ и WR. При отключении или точнее изоляции их от питающих напряжений возможно кратковременное хранение информации, как в ячейке динамической памяти, при этом возможна также перезапись. Данные снимаются при чтении или подаются во время записи прямо с/на среднюю точку. С этого в принципе все началось.

Для использования триггера в матрице запоминающего устройства необходимы для каждой ячейки дополнительно четыре (рис. 1б) или три (рис. 1в) ключа для выборки по координатным осям и управления записью.

В этом случае питание подается через сигналы WR’ и WR. При отключении или точнее изоляции их от питающих напряжений возможно кратковременное хранение информации, как в ячейке динамической памяти, при этом возможна также перезапись. Данные снимаются при чтении или подаются во время записи прямо с/на среднюю точку. С этого в принципе все началось.

Для использования триггера в матрице запоминающего устройства необходимы для каждой ячейки дополнительно четыре (рис. 1б) или три (рис. 1в) ключа для выборки по координатным осям и управления записью.

Рис. 1, 2: Примеры реализации ячеек памяти на ключах (SW), в качестве которых обычно используются полевые транзисторы.

Рис. 1, 2: Примеры реализации ячеек памяти на ключах (SW), в качестве которых обычно используются полевые транзисторы.

Рис. 3: Полевой двухзатворный транзистор, позволяющий скомпоновать два транзистора в один.

Возможна реализация подобной ячейки на КМДП-транзисторах со встроенным каналом. Ключи обрамления могут представлять собой обычные КМДП-транзисторы с индуцированным каналом, реализация которых особенно проста. Для реализации на КМДП-транзисторах с индуцированным каналом необходимо добавить еще один каскад (рис.2а, на рис. 2б показана схема с дополнительными ключами для двухкоординатной выборки). Ключи для двухкоординатной выборки и дополнительные ключи на рис. 1б могут быть при применении двухзатворных МДП-транзисторов с последовательно расположенными затворами (рис.3) сгруппированы попарно, что уменьшит количество ключей или транзисторов для ячейки на рис. 1б до трех.

Второе: разложить все по кирпичикам дальше. Как видно, каскады на фиг. 1 представляют собой формирователи без инверсии, а на фиг. 2 — инверторы, в результате получаем схемы на фиг. 4. На фиг. 4а и 4б нижние ключи нарисованы с инверсным управлением.

Рис. 3: Полевой двухзатворный транзистор, позволяющий скомпоновать два транзистора в один.

Возможна реализация подобной ячейки на КМДП-транзисторах со встроенным каналом. Ключи обрамления могут представлять собой обычные КМДП-транзисторы с индуцированным каналом, реализация которых особенно проста. Для реализации на КМДП-транзисторах с индуцированным каналом необходимо добавить еще один каскад (рис.2а, на рис. 2б показана схема с дополнительными ключами для двухкоординатной выборки). Ключи для двухкоординатной выборки и дополнительные ключи на рис. 1б могут быть при применении двухзатворных МДП-транзисторов с последовательно расположенными затворами (рис.3) сгруппированы попарно, что уменьшит количество ключей или транзисторов для ячейки на рис. 1б до трех.

Второе: разложить все по кирпичикам дальше. Как видно, каскады на фиг. 1 представляют собой формирователи без инверсии, а на фиг. 2 — инверторы, в результате получаем схемы на фиг. 4. На фиг. 4а и 4б нижние ключи нарисованы с инверсным управлением.

Рис. 4: Дополнительные примеры реализации ячеек статической памяти на инверторах и прямых формирователях, позволяющие не устраивать конфликты на шинах.

Для возможности объединения ключей с помощью двухзатворных транзисторов, т.е. при отсутствии оной они могут быть и с прямыми входами.

В отдаленной перспективе, если указанные схемы используются в устройствах с иным принципом действия, например на биполярных транзисторах или оптических ключах, то при отсутствии эффекта емкости на входах элементов необходимо сигналы WR и WR’ тоже подавать через схемы управления, аналогично линии DIO (один разрешающий ключ для регистра или последовательные два ключа для двукоординатной выборки).

В итоге получаем чуть ли не идеал регистровой памяти на любой вкус по цене динамической. Конечно же при наличии желания производителя! А если на этот раз уже принять внимание упомянутые недостатки специфического интерфейса динамической памяти и протокола общения с ней, которые вносят свою лепту в увеличение тока потребления системы, а так же в ограничение ее быстродействия, то получаем … Нет я не буду дальше продолжать из-за скромности! Предложу это сделать читателю, так как понимаю, что я не один, что дальше возможно находятся еще неизведанные пространства познания и читатель тоже наверняка хочет почувствовать радость первооткрывателя.

1. Принципы функционирования SRAM. Крис Касперски (Ссылка citforum.ru/book/optimize/sdram.shtml );

2. D-триггер или ячейка регистра/памяти (Ссылка timeinventor.com/news.php?readmore=118 ).

Ссылки:

1. http://timeinventor.com/news.php?readmore=118 ;

2. http://technic.itizdat.ru/docs/mer/FIL13208061890N727706001/ ;

3. http://www.membrana.ru/particle/17550 .

Рис. 4: Дополнительные примеры реализации ячеек статической памяти на инверторах и прямых формирователях, позволяющие не устраивать конфликты на шинах.

Для возможности объединения ключей с помощью двухзатворных транзисторов, т.е. при отсутствии оной они могут быть и с прямыми входами.

В отдаленной перспективе, если указанные схемы используются в устройствах с иным принципом действия, например на биполярных транзисторах или оптических ключах, то при отсутствии эффекта емкости на входах элементов необходимо сигналы WR и WR’ тоже подавать через схемы управления, аналогично линии DIO (один разрешающий ключ для регистра или последовательные два ключа для двукоординатной выборки).

В итоге получаем чуть ли не идеал регистровой памяти на любой вкус по цене динамической. Конечно же при наличии желания производителя! А если на этот раз уже принять внимание упомянутые недостатки специфического интерфейса динамической памяти и протокола общения с ней, которые вносят свою лепту в увеличение тока потребления системы, а так же в ограничение ее быстродействия, то получаем … Нет я не буду дальше продолжать из-за скромности! Предложу это сделать читателю, так как понимаю, что я не один, что дальше возможно находятся еще неизведанные пространства познания и читатель тоже наверняка хочет почувствовать радость первооткрывателя.

1. Принципы функционирования SRAM. Крис Касперски (Ссылка citforum.ru/book/optimize/sdram.shtml );

2. D-триггер или ячейка регистра/памяти (Ссылка timeinventor.com/news.php?readmore=118 ).

Ссылки:

1. http://timeinventor.com/news.php?readmore=118 ;

2. http://technic.itizdat.ru/docs/mer/FIL13208061890N727706001/ ;

3. http://www.membrana.ru/particle/17550 .